Arhitekture za obradu signala i slike

Sinopsis:

Zajedničko istraživanje sa Fakultetom Računarstva i informatike Ljubljana, Slovenija, podržano od strane Slovenian Research Agency (ARRS) i Ministarstva civilnih poslova BiH

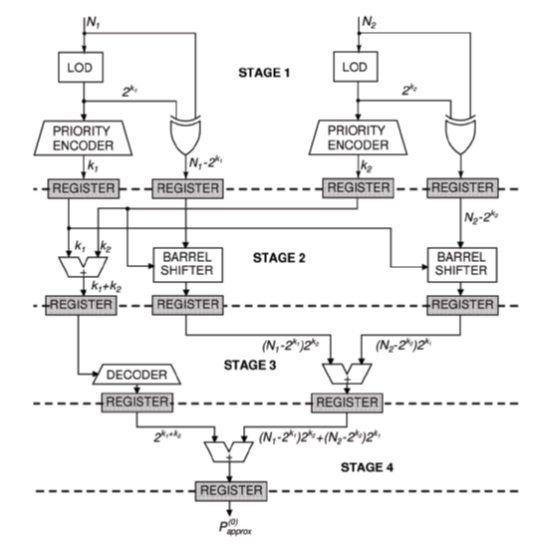

U mnogim primjenama digitalne obrade signala efikasne implementacije sa malim kašnjenjima signala su značajnije od visoke tačnosti izračunavanja. Predmet ovog istraživanja su arhitekture za koje koriste iterativne algoritme i jednostavna kombinatorna kola da bi se dobile efikasne implementacije algoritama za obradu signala i slike.

Radovi:

- A. Avramovic, Z. Babic, D. Raic, D. Strle, P. Bulic, "An approximate logarithmic squaring circuit with error compensation for DSP applications", Microelectronics Journal 45 (3), 263-271, 2014

- Babic, Z., Avramovic, A., P. Bulic: An Iterative Logarithmic Multiplier, Microprocessors and Microsystems 35 (1) , pp. 23-33, 2011.

- Risojevic, V., Avramovic, A., Babic, Z., P. Bulic: A simple pipelined squaring circuit for DSP, ICCD 2011, Amherst, USA.

- Avramovic, A. ,P. Bulic, Babic, Z.: Digital Sgnal Processing Applications with Iterative Logarithmic Multipliers, JITA 1 (2) , pp. 83-89, 2011. Banja Luka.

- P. Bulic, Babic, Z., Avramovic, A.: A Simple Pipelined Logarithmic Multiplier, ICCD 2010, Amsterdam.

- Babic, Z., Avramovic, A., P. Bulic: An Iterative Mitchell's Algorithm Based Multiplier, ISSPIT 2008, Sarajevo.